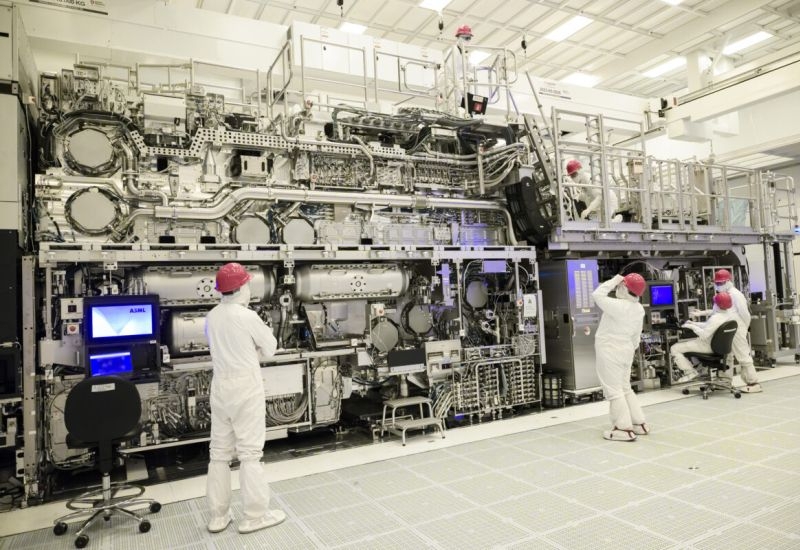

Компания Intel стала одним из первых получателей литографических сканеров ASML класса High-NA EUV, позволяющих наладить выпуск чипов по нормам тоньше 2 нм, но если ранее это были системы первого поколения, пригодные главным образом для экспериментов, то недавно завершились приёмочные испытания Twinscan EXE:5200B — сканера, который будет использоваться в серийном производстве чипов.

HUAWEI XMAGE 2025: мобильная фотография как полноценное окно в мир искусства

HUAWEI FreeBuds 7i: ставка на глубину

Российские итоги HUAWEI XMAGE 2025 и выставка «Фото[графическое] путешествие»

На 3DNews началось голосование за лучшую игру 2025 года

Смартфон HUAWEI Pura 80 Pro как универсальный инструмент тревел-фотографа

Видеообзор смартфона Honor X9d

Пять причин полюбить HONOR Magic 7

Процессоры за 30 тысяч рублей — большой сравнительный тест

Топ-10 смартфонов до 20 тысяч рублей (2025 год)

Новой системе свойственно высокое разрешение, проверенное ещё на предшественнике (Twinscan EXE:5000), но производительность обработки кремниевых пластин повышена до 175 штук в час, а точность наложения слоёв при экспозиции увеличена до 0,7 нанометра. Оборудование ASML для сверхжёсткой ультрафиолетовой литографии с высокой числовой апертурой (High-NA EUV) тестировалось компанией Intel с 2023 года, но модель Twinscan EXE:5200B обеспечивает ряд преимуществ по сравнению с ранними образцами.

Более мощный источник лазерного излучения обеспечивает создание более контрастных проекций с более чёткими очертаниями будущих транзисторов. Новая конструкция держателя для кремниевых пластин учитывает особенности техпроцесса их обработки, повышая пропускную способность в условиях массового производства. Возросшая точность наложения была достигнута за счёт лучшей калибровки датчиков, стабильности основания и изоляции от окружающих воздействий.

Оборудование нового поколения позволяет сократить количество операций при изготовлении передовых чипов, уменьшить затраты на оснастку и поднять производительность линии. Само собой, уровень брака должен выходить на приемлемый уровень быстрее, чем в случае с оборудованием предыдущего поколения.

Попутно представители Intel сообщили о прогрессе в сфере внедрения новых материалов при производстве чипов с мельчайшими транзисторами. Дихалькогениды переходных металлов, по их словам, позволяют создавать структуры размером с несколько атомов кремния без угрозы потери необходимых физических свойств. В сфере совершенствования двумерных материалов Intel активно сотрудничает с Imec — ведущей европейской исследовательской организацией. Партнёры добиваются определённого прогресса во внедрении новых материалов, применение которых возможно и целесообразно в условиях массового производства с типоразмером кремниевых пластин 300 мм.

В свою очередь, ASML планирует наладить массовые поставки оборудования класса High-NA EUV с 2027 года, но для этого уже в следующем году компании придётся плотно взаимодействовать в этой сфере со своими клиентами. В следующем десятилетии ASML предложит технологию Hyper-NA, которая обещает ещё более эффективное масштабирование транзисторов на поверхности чипа и сохранение приемлемых темпов роста производительности полупроводниковых компонентов.

Добавить комментарий