JEDEC анонсировала план развития стандарта памяти LPDDR6 с плотностью до 512 Гбайт на модуль и раскрыла детали сразу двух стандартов в разработке — модульного SOCAMM2 и технологии вычислений в памяти PIM. Новый стандарт расширяет применение LPDDR6 за пределы мобильных платформ и нацелен на ЦОД и вычисления для задач ИИ.

От Ryzen 7 1800X до Ryzen 7 9850X3D: девять лет эволюции AMD в одном тесте

Обзор Ryzen 7 9850X3D: три процента за двадцать баксов

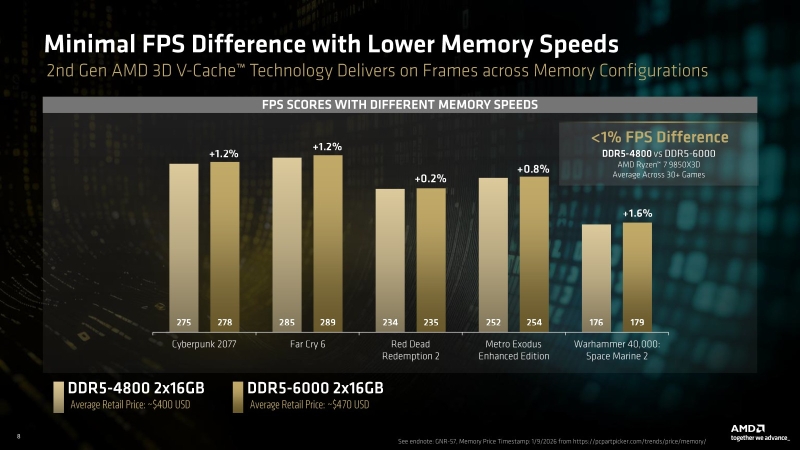

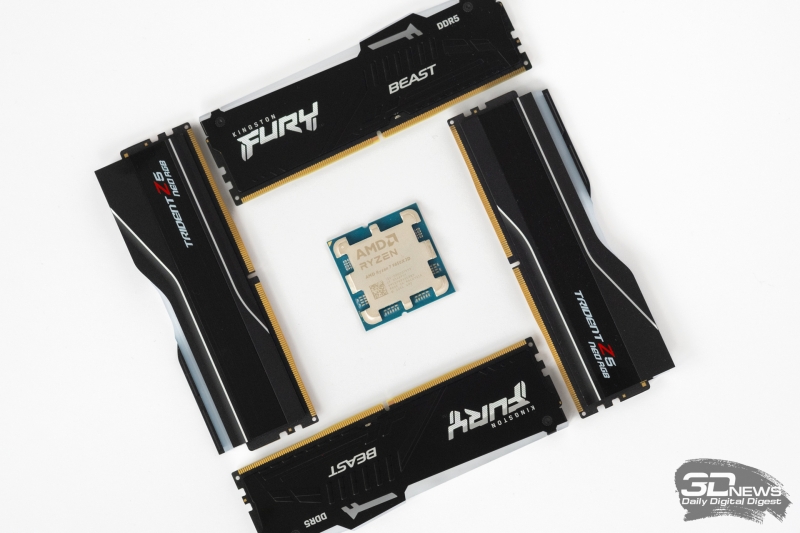

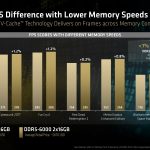

Можно ли экономить на DDR5 для Ryzen? Сравниваем дешёвую память с дорогой

Обзор Apple MacBook Neo: удивительно хороший ноутбук с процессором от iPhone

Обзор Samsung Galaxy Z TriFold: тройной складной смартфон по цене квартиры в Воркуте

Компьютер месяца, спецвыпуск: эпоха отката, или Как дефицит чипов памяти влияет на выбор железа для игрового ПК

Обзор ноутбука HONOR MagicBook X16 2026: как раньше, только лучше

Ryzen и 16 Гбайт DDR5: как сэкономить на памяти так, чтобы не лишиться 15 % производительности

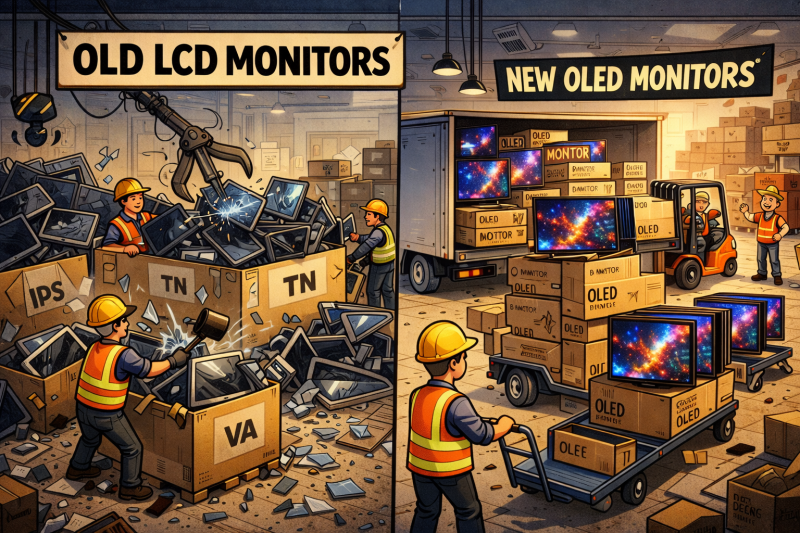

Гид по выбору OLED-монитора в 2026 году: эволюция в деталях

Организация строит следующую версию стандарта JESD209‑6 на базе спецификации, опубликованной в июле 2025 года. Ключевое архитектурное изменение — переход к небинарной ширине интерфейса на кристалл: вместо прежнего x16 стандарт вводит режимы x24, x12 и x6. Более узкий субканальный режим x6 позволяет разместить больше кристаллов в одном корпусе и тем самым нарастить ёмкость памяти на компонент и на канал — что критично для масштабирования под нагрузки ИИ.

Параллельно стандарт получит механизм гибкого резервирования метаданных с минимальным влиянием на пиковую пропускную способность. Клиенты из сектора ЦОД смогут самостоятельно регулировать баланс между пользовательской ёмкостью и объёмом метаданных в зависимости от требований к надёжности конкретной системы. Ожидаемый потолок плотности LPDDR6 превысит нынешний максимум LPDDR5/5X и достигнет 512 Гбайт на модуль. JEDEC называет это достижение ответом на растущие запросы к объёму памяти при обучении и инференсе ИИ-моделей.

Подкомитет JC‑42.6 ведёт разработку двух сопутствующих стандартов. Первый — модульный стандарт LPDDR6 SOCAMM2, который сохранит компактный и заменяемый формфактор и обеспечит чёткий путь обновления с нынешних модулей LPDDR5X SOCAMM2. Второй — стандарт вычислений в памяти LPDDR6 PIM (Processing-in-Memory): его разработка близится к завершению. Стандарт ориентирован на инференс на периферии и в ЦОД, где требования к производительности и энергоэффективности быстро растут. Технология встраивает вычислительные блоки непосредственно в память LPDDR6, сокращает перемещение данных между памятью и вычислительными блоками и за счёт этого повышает производительность инференса при меньшем энергопотреблении — не жертвуя энергоэффективностью платформы LPDDR.

Добавить комментарий